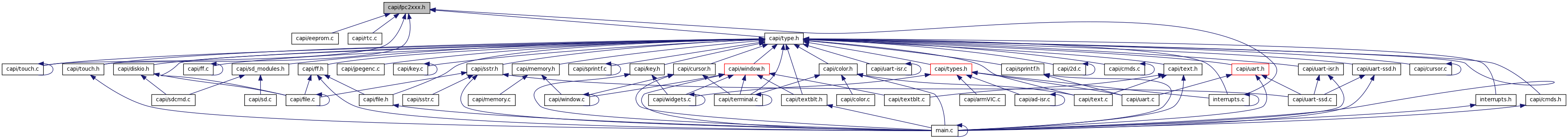

capi/lpc2xxx.h File Reference

Go to the source code of this file.

Defines | |

| #define | BCFG0 (*((volatile unsigned int *) 0xFFE00000)) |

| #define | BCFG1 (*((volatile unsigned int *) 0xFFE00004)) |

| #define | BCFG2 (*((volatile unsigned int *) 0xFFE00008)) |

| #define | BCFG3 (*((volatile unsigned int *) 0xFFE0000C)) |

| #define | EXTINT (*((volatile unsigned char *) 0xE01FC140)) |

| #define | EXTWAKE (*((volatile unsigned char *) 0xE01FC144)) |

| #define | EXTMODE (*((volatile unsigned char *) 0xE01FC148)) |

| #define | EXTPOLAR (*((volatile unsigned char *) 0xE01FC14C)) |

| #define | MEMMAP (*((volatile unsigned char *) 0xE01FC040)) |

| #define | PLLCON (*((volatile unsigned char *) 0xE01FC080)) |

| #define | PLLCFG (*((volatile unsigned char *) 0xE01FC084)) |

| #define | PLLSTAT (*((volatile unsigned short*) 0xE01FC088)) |

| #define | PLLFEED (*((volatile unsigned char *) 0xE01FC08C)) |

| #define | PCON (*((volatile unsigned char *) 0xE01FC0C0)) |

| #define | PCONP (*((volatile unsigned long *) 0xE01FC0C4)) |

| #define | VPBDIV (*((volatile unsigned char *) 0xE01FC100)) |

| #define | APBDIV (*((volatile unsigned char *) 0xE01FC100)) |

| #define | MAMCR (*((volatile unsigned char *) 0xE01FC000)) |

| #define | MAMTIM (*((volatile unsigned char *) 0xE01FC004)) |

| #define | VICIRQStatus (*((volatile unsigned long *) 0xFFFFF000)) |

| #define | VICFIQStatus (*((volatile unsigned long *) 0xFFFFF004)) |

| #define | VICRawIntr (*((volatile unsigned long *) 0xFFFFF008)) |

| #define | VICIntSelect (*((volatile unsigned long *) 0xFFFFF00C)) |

| #define | VICIntEnable (*((volatile unsigned long *) 0xFFFFF010)) |

| #define | VICIntEnClr (*((volatile unsigned long *) 0xFFFFF014)) |

| #define | VICSoftInt (*((volatile unsigned long *) 0xFFFFF018)) |

| #define | VICSoftIntClear (*((volatile unsigned long *) 0xFFFFF01C)) |

| #define | VICProtection (*((volatile unsigned long *) 0xFFFFF020)) |

| #define | VICVectAddr (*((volatile unsigned long *) 0xFFFFF030)) |

| #define | VICDefVectAddr (*((volatile unsigned long *) 0xFFFFF034)) |

| #define | VICVectAddr0 (*((volatile unsigned long *) 0xFFFFF100)) |

| #define | VICVectAddr1 (*((volatile unsigned long *) 0xFFFFF104)) |

| #define | VICVectAddr2 (*((volatile unsigned long *) 0xFFFFF108)) |

| #define | VICVectAddr3 (*((volatile unsigned long *) 0xFFFFF10C)) |

| #define | VICVectAddr4 (*((volatile unsigned long *) 0xFFFFF110)) |

| #define | VICVectAddr5 (*((volatile unsigned long *) 0xFFFFF114)) |

| #define | VICVectAddr6 (*((volatile unsigned long *) 0xFFFFF118)) |

| #define | VICVectAddr7 (*((volatile unsigned long *) 0xFFFFF11C)) |

| #define | VICVectAddr8 (*((volatile unsigned long *) 0xFFFFF120)) |

| #define | VICVectAddr9 (*((volatile unsigned long *) 0xFFFFF124)) |

| #define | VICVectAddr10 (*((volatile unsigned long *) 0xFFFFF128)) |

| #define | VICVectAddr11 (*((volatile unsigned long *) 0xFFFFF12C)) |

| #define | VICVectAddr12 (*((volatile unsigned long *) 0xFFFFF130)) |

| #define | VICVectAddr13 (*((volatile unsigned long *) 0xFFFFF134)) |

| #define | VICVectAddr14 (*((volatile unsigned long *) 0xFFFFF138)) |

| #define | VICVectAddr15 (*((volatile unsigned long *) 0xFFFFF13C)) |

| #define | VICVectCntl0 (*((volatile unsigned long *) 0xFFFFF200)) |

| #define | VICVectCntl1 (*((volatile unsigned long *) 0xFFFFF204)) |

| #define | VICVectCntl2 (*((volatile unsigned long *) 0xFFFFF208)) |

| #define | VICVectCntl3 (*((volatile unsigned long *) 0xFFFFF20C)) |

| #define | VICVectCntl4 (*((volatile unsigned long *) 0xFFFFF210)) |

| #define | VICVectCntl5 (*((volatile unsigned long *) 0xFFFFF214)) |

| #define | VICVectCntl6 (*((volatile unsigned long *) 0xFFFFF218)) |

| #define | VICVectCntl7 (*((volatile unsigned long *) 0xFFFFF21C)) |

| #define | VICVectCntl8 (*((volatile unsigned long *) 0xFFFFF220)) |

| #define | VICVectCntl9 (*((volatile unsigned long *) 0xFFFFF224)) |

| #define | VICVectCntl10 (*((volatile unsigned long *) 0xFFFFF228)) |

| #define | VICVectCntl11 (*((volatile unsigned long *) 0xFFFFF22C)) |

| #define | VICVectCntl12 (*((volatile unsigned long *) 0xFFFFF230)) |

| #define | VICVectCntl13 (*((volatile unsigned long *) 0xFFFFF234)) |

| #define | VICVectCntl14 (*((volatile unsigned long *) 0xFFFFF238)) |

| #define | VICVectCntl15 (*((volatile unsigned long *) 0xFFFFF23C)) |

| #define | VIC_WDT 0 |

| #define | VIC_ARMCore0 2 |

| #define | VIC_ARMCore1 3 |

| #define | VIC_TIMER0 4 |

| #define | VIC_TIMER1 5 |

| #define | VIC_UART0 6 |

| #define | VIC_UART1 7 |

| #define | VIC_PWM 8 |

| #define | VIC_PWM0 8 |

| #define | VIC_I2C0 9 |

| #define | VIC_SPI 10 |

| #define | VIC_SPI0 10 |

| #define | VIC_SPI1 11 |

| #define | VIC_PLL 12 |

| #define | VIC_RTC 13 |

| #define | VIC_EINT0 14 |

| #define | VIC_EINT1 15 |

| #define | VIC_EINT2 16 |

| #define | VIC_EINT3 17 |

| #define | VIC_AD0 18 |

| #define | VIC_I2C1 19 |

| #define | VIC_BOD 20 |

| #define | VIC_AD1 21 |

| #define | VIC_USB 22 |

| #define | VIC_TIMER2 26 |

| #define | VIC_TIMER3 27 |

| #define | VIC_CAN 19 |

| #define | VIC_CAN1_TX 20 |

| #define | VIC_CAN2_TX 21 |

| #define | VIC_CAN1_RX 26 |

| #define | VIC_CAN2_RX 27 |

| #define | VIC_ENABLE (1 << 5) |

| #define | VIC_BIT(chan) (1 << (chan)) |

| #define | PINSEL0 (*((volatile unsigned long *) 0xE002C000)) |

| #define | PINSEL1 (*((volatile unsigned long *) 0xE002C004)) |

| #define | PINSEL2 (*((volatile unsigned long *) 0xE002C014)) |

| #define | LPC210X_FAST_GPIO |

| #define | IOPIN (*((volatile unsigned long *) 0xE0028000)) |

| #define | IOSET (*((volatile unsigned long *) 0xE0028004)) |

| #define | IODIR (*((volatile unsigned long *) 0xE0028008)) |

| #define | IOCLR (*((volatile unsigned long *) 0xE002800C)) |

| #define | FIOMASK (*((volatile unsigned long *) 0x3FFFC010)) |

| #define | FIOSET (*((volatile unsigned long *) 0x3FFFC018)) |

| #define | FIOCLR (*((volatile unsigned long *) 0x3FFFC01C)) |

| #define | FIOPIN (*((volatile unsigned long *) 0x3FFFC014)) |

| #define | IO0PIN (*((volatile unsigned long *) 0xE0028000)) |

| #define | IO0SET (*((volatile unsigned long *) 0xE0028004)) |

| #define | IO0DIR (*((volatile unsigned long *) 0xE0028008)) |

| #define | IO0CLR (*((volatile unsigned long *) 0xE002800C)) |

| #define | IO1PIN (*((volatile unsigned long *) 0xE0028010)) |

| #define | IO1SET (*((volatile unsigned long *) 0xE0028014)) |

| #define | IO1DIR (*((volatile unsigned long *) 0xE0028018)) |

| #define | IO1CLR (*((volatile unsigned long *) 0xE002801C)) |

| #define | IO2PIN (*((volatile unsigned long *) 0xE0028020)) |

| #define | IO2SET (*((volatile unsigned long *) 0xE0028024)) |

| #define | IO2DIR (*((volatile unsigned long *) 0xE0028028)) |

| #define | IO2CLR (*((volatile unsigned long *) 0xE002802C)) |

| #define | IO3PIN (*((volatile unsigned long *) 0xE0028030)) |

| #define | IO3SET (*((volatile unsigned long *) 0xE0028034)) |

| #define | IO3DIR (*((volatile unsigned long *) 0xE0028038)) |

| #define | IO3CLR (*((volatile unsigned long *) 0xE002803C)) |

| #define | U0RBR (*((volatile unsigned char *) 0xE000C000)) |

| #define | U0THR (*((volatile unsigned char *) 0xE000C000)) |

| #define | U0IER (*((volatile unsigned char *) 0xE000C004)) |

| #define | U0IIR (*((volatile unsigned char *) 0xE000C008)) |

| #define | U0FCR (*((volatile unsigned char *) 0xE000C008)) |

| #define | U0LCR (*((volatile unsigned char *) 0xE000C00C)) |

| #define | U0LSR (*((volatile unsigned char *) 0xE000C014)) |

| #define | U0SCR (*((volatile unsigned char *) 0xE000C01C)) |

| #define | U0DLL (*((volatile unsigned char *) 0xE000C000)) |

| #define | U0DLM (*((volatile unsigned char *) 0xE000C004)) |

| #define | U0ACR (*((volatile unsigned char *) 0xE000C020)) |

| #define | U0FDR (*((volatile unsigned char *) 0xE000C028)) |

| #define | U0TER (*((volatile unsigned char *) 0xE000C030)) |

| #define | U1RBR (*((volatile unsigned char *) 0xE0010000)) |

| #define | U1THR (*((volatile unsigned char *) 0xE0010000)) |

| #define | U1IER (*((volatile unsigned char *) 0xE0010004)) |

| #define | U1IIR (*((volatile unsigned char *) 0xE0010008)) |

| #define | U1FCR (*((volatile unsigned char *) 0xE0010008)) |

| #define | U1LCR (*((volatile unsigned char *) 0xE001000C)) |

| #define | U1MCR (*((volatile unsigned char *) 0xE0010010)) |

| #define | U1LSR (*((volatile unsigned char *) 0xE0010014)) |

| #define | U1MSR (*((volatile unsigned char *) 0xE0010018)) |

| #define | U1SCR (*((volatile unsigned char *) 0xE001001C)) |

| #define | U1DLL (*((volatile unsigned char *) 0xE0010000)) |

| #define | U1DLM (*((volatile unsigned char *) 0xE0010004)) |

| #define | UIER_ERBFI (1 << 0) |

| #define | UIER_ETBEI (1 << 1) |

| #define | UIER_ELSI (1 << 2) |

| #define | UIER_EDSSI (1 << 3) |

| #define | UIIR_NO_INT (1 << 0) |

| #define | UIIR_MS_INT (0 << 1) |

| #define | UIIR_THRE_INT (1 << 1) |

| #define | UIIR_RDA_INT (2 << 1) |

| #define | UIIR_RLS_INT (3 << 1) |

| #define | UIIR_CTI_INT (6 << 1) |

| #define | UIIR_ID_MASK 0x0E |

| #define | UFCR_FIFO_ENABLE (1 << 0) |

| #define | UFCR_RX_FIFO_RESET (1 << 1) |

| #define | UFCR_TX_FIFO_RESET (1 << 2) |

| #define | UFCR_FIFO_TRIG1 (0 << 6) |

| #define | UFCR_FIFO_TRIG4 (1 << 6) |

| #define | UFCR_FIFO_TRIG8 (2 << 6) |

| #define | UFCR_FIFO_TRIG14 (3 << 6) |

| #define | ULCR_CHAR_5 (0 << 0) |

| #define | ULCR_CHAR_6 (1 << 0) |

| #define | ULCR_CHAR_7 (2 << 0) |

| #define | ULCR_CHAR_8 (3 << 0) |

| #define | ULCR_STOP_1 (0 << 2) |

| #define | ULCR_STOP_2 (1 << 2) |

| #define | ULCR_PAR_NO (0 << 3) |

| #define | ULCR_PAR_ODD (1 << 3) |

| #define | ULCR_PAR_EVEN (3 << 3) |

| #define | ULCR_PAR_MARK (5 << 3) |

| #define | ULCR_PAR_SPACE (7 << 3) |

| #define | ULCR_BREAK_ENABLE (1 << 6) |

| #define | ULCR_DLAB_ENABLE (1 << 7) |

| #define | UMCR_DTR (1 << 0) |

| #define | UMCR_RTS (1 << 1) |

| #define | UMCR_LB (1 << 4) |

| #define | ULSR_RDR (1 << 0) |

| #define | ULSR_OE (1 << 1) |

| #define | ULSR_PE (1 << 2) |

| #define | ULSR_FE (1 << 3) |

| #define | ULSR_BI (1 << 4) |

| #define | ULSR_THRE (1 << 5) |

| #define | ULSR_TEMT (1 << 6) |

| #define | ULSR_RXFE (1 << 7) |

| #define | ULSR_ERR_MASK 0x1E |

| #define | UMSR_DCTS (1 << 0) |

| #define | UMSR_DDSR (1 << 1) |

| #define | UMSR_TERI (1 << 2) |

| #define | UMSR_DDCD (1 << 3) |

| #define | UMSR_CTS (1 << 4) |

| #define | UMSR_DSR (1 << 5) |

| #define | UMSR_RI (1 << 6) |

| #define | UMSR_DCD (1 << 7) |

| #define | I2CONSET (*((volatile unsigned char *) 0xE001C000)) |

| #define | I2STAT (*((volatile unsigned char *) 0xE001C004)) |

| #define | I2DAT (*((volatile unsigned char *) 0xE001C008)) |

| #define | I2ADR (*((volatile unsigned char *) 0xE001C00C)) |

| #define | I2SCLH (*((volatile unsigned short *) 0xE001C010)) |

| #define | I2SCLL (*((volatile unsigned short *) 0xE001C014)) |

| #define | I2CONCLR (*((volatile unsigned char *) 0xE001C018)) |

| #define | I2AA 0x04 |

| #define | I2SI 0x08 |

| #define | I2STO 0x10 |

| #define | I2STA 0x20 |

| #define | I2EN 0x40 |

| #define | SPI_SPCR (*((volatile unsigned char *) 0xE0020000)) |

| #define | SPI_SPSR (*((volatile unsigned char *) 0xE0020004)) |

| #define | SPI_SPDR (*((volatile unsigned char *) 0xE0020008)) |

| #define | SPI_SPCCR (*((volatile unsigned char *) 0xE002000C)) |

| #define | SPI_SPINT (*((volatile unsigned char *) 0xE002001C)) |

| #define | S0PCR (*((volatile unsigned char *) 0xE0020000)) |

| #define | S0PSR (*((volatile unsigned char *) 0xE0020004)) |

| #define | S0PDR (*((volatile unsigned char *) 0xE0020008)) |

| #define | S0PCCR (*((volatile unsigned char *) 0xE002000C)) |

| #define | S0PINT (*((volatile unsigned char *) 0xE002001C)) |

| #define | S1PCR (*((volatile unsigned char *) 0xE0030000)) |

| #define | S1PSR (*((volatile unsigned char *) 0xE0030004)) |

| #define | S1PDR (*((volatile unsigned char *) 0xE0030008)) |

| #define | S1PCCR (*((volatile unsigned char *) 0xE003000C)) |

| #define | S1PINT (*((volatile unsigned char *) 0xE003001C)) |

| #define | CAN1MOD (*((volatile unsigned long *) 0xE0044000)) |

| #define | CAN1CMR (*((volatile unsigned long *) 0xE0044004)) |

| #define | CAN1GSR (*((volatile unsigned long *) 0xE0044008)) |

| #define | CAN1ICR (*((volatile unsigned long *) 0xE004400C)) |

| #define | CAN1IER (*((volatile unsigned long *) 0xE0044010)) |

| #define | CAN1BTR (*((volatile unsigned long *) 0xE0044014)) |

| #define | CAN1EWL (*((volatile unsigned long *) 0xE004401C)) |

| #define | CAN1SR (*((volatile unsigned long *) 0xE0044020)) |

| #define | CAN1RFS (*((volatile unsigned long *) 0xE0044024)) |

| #define | CAN1RDA (*((volatile unsigned long *) 0xE0044028)) |

| #define | CAN1RDB (*((volatile unsigned long *) 0xE004402C)) |

| #define | CAN1TFI1 (*((volatile unsigned long *) 0xE0044030)) |

| #define | CAN1TID1 (*((volatile unsigned long *) 0xE0044034)) |

| #define | CAN1TDA1 (*((volatile unsigned long *) 0xE0044038)) |

| #define | CAN1TDB1 (*((volatile unsigned long *) 0xE004403C)) |

| #define | CAN1TFI2 (*((volatile unsigned long *) 0xE0044040)) |

| #define | CAN1TID2 (*((volatile unsigned long *) 0xE0044044)) |

| #define | CAN1TDA2 (*((volatile unsigned long *) 0xE0044048)) |

| #define | CAN1TDB2 (*((volatile unsigned long *) 0xE004404C)) |

| #define | CAN1TFI3 (*((volatile unsigned long *) 0xE0044050)) |

| #define | CAN1TID3 (*((volatile unsigned long *) 0xE0044054)) |

| #define | CAN1TDA3 (*((volatile unsigned long *) 0xE0044058)) |

| #define | CAN1TDB3 (*((volatile unsigned long *) 0xE004405C)) |

| #define | CAN2MOD (*((volatile unsigned long *) 0xE0048000)) |

| #define | CAN2CMR (*((volatile unsigned long *) 0xE0048004)) |

| #define | CAN2GSR (*((volatile unsigned long *) 0xE0048008)) |

| #define | CAN2ICR (*((volatile unsigned long *) 0xE004800C)) |

| #define | CAN2IER (*((volatile unsigned long *) 0xE0048010)) |

| #define | CAN2BTR (*((volatile unsigned long *) 0xE0048014)) |

| #define | CAN2EWL (*((volatile unsigned long *) 0xE004801C)) |

| #define | CAN2SR (*((volatile unsigned long *) 0xE0048020)) |

| #define | CAN2RFS (*((volatile unsigned long *) 0xE0048024)) |

| #define | CAN2RDA (*((volatile unsigned long *) 0xE0048028)) |

| #define | CAN2RDB (*((volatile unsigned long *) 0xE004802C)) |

| #define | CAN2TFI1 (*((volatile unsigned long *) 0xE0048030)) |

| #define | CAN2TID1 (*((volatile unsigned long *) 0xE0048034)) |

| #define | CAN2TDA1 (*((volatile unsigned long *) 0xE0048038)) |

| #define | CAN2TDB1 (*((volatile unsigned long *) 0xE004803C)) |

| #define | CAN2TFI2 (*((volatile unsigned long *) 0xE0048040)) |

| #define | CAN2TID2 (*((volatile unsigned long *) 0xE0048044)) |

| #define | CAN2TDA2 (*((volatile unsigned long *) 0xE0048048)) |

| #define | CAN2TDB2 (*((volatile unsigned long *) 0xE004804C)) |

| #define | CAN2TFI3 (*((volatile unsigned long *) 0xE0048050)) |

| #define | CAN2TID3 (*((volatile unsigned long *) 0xE0048054)) |

| #define | CAN2TDA3 (*((volatile unsigned long *) 0xE0048058)) |

| #define | CAN2TDB3 (*((volatile unsigned long *) 0xE004805C)) |

| #define | CAN3MOD (*((volatile unsigned long *) 0xE004C000)) |

| #define | CAN3CMR (*((volatile unsigned long *) 0xE004C004)) |

| #define | CAN3GSR (*((volatile unsigned long *) 0xE004C008)) |

| #define | CAN3ICR (*((volatile unsigned long *) 0xE004C00C)) |

| #define | CAN3IER (*((volatile unsigned long *) 0xE004C010)) |

| #define | CAN3BTR (*((volatile unsigned long *) 0xE004C014)) |

| #define | CAN3EWL (*((volatile unsigned long *) 0xE004C01C)) |

| #define | CAN3SR (*((volatile unsigned long *) 0xE004C020)) |

| #define | CAN3RFS (*((volatile unsigned long *) 0xE004C024)) |

| #define | CAN3RDA (*((volatile unsigned long *) 0xE004C028)) |

| #define | CAN3RDB (*((volatile unsigned long *) 0xE004C02C)) |

| #define | CAN3TFI1 (*((volatile unsigned long *) 0xE004C030)) |

| #define | CAN3TID1 (*((volatile unsigned long *) 0xE004C034)) |

| #define | CAN3TDA1 (*((volatile unsigned long *) 0xE004C038)) |

| #define | CAN3TDB1 (*((volatile unsigned long *) 0xE004C03C)) |

| #define | CAN3TFI2 (*((volatile unsigned long *) 0xE004C040)) |

| #define | CAN3TID2 (*((volatile unsigned long *) 0xE004C044)) |

| #define | CAN3TDA2 (*((volatile unsigned long *) 0xE004C048)) |

| #define | CAN3TDB2 (*((volatile unsigned long *) 0xE004C04C)) |

| #define | CAN3TFI3 (*((volatile unsigned long *) 0xE004C050)) |

| #define | CAN3TID3 (*((volatile unsigned long *) 0xE004C054)) |

| #define | CAN3TDA3 (*((volatile unsigned long *) 0xE004C058)) |

| #define | CAN3TDB3 (*((volatile unsigned long *) 0xE004C05C)) |

| #define | CAN4MOD (*((volatile unsigned long *) 0xE0050000)) |

| #define | CAN4CMR (*((volatile unsigned long *) 0xE0050004)) |

| #define | CAN4GSR (*((volatile unsigned long *) 0xE0050008)) |

| #define | CAN4ICR (*((volatile unsigned long *) 0xE005000C)) |

| #define | CAN4IER (*((volatile unsigned long *) 0xE0050010)) |

| #define | CAN4BTR (*((volatile unsigned long *) 0xE0050014)) |

| #define | CAN4EWL (*((volatile unsigned long *) 0xE005001C)) |

| #define | CAN4SR (*((volatile unsigned long *) 0xE0050020)) |

| #define | CAN4RFS (*((volatile unsigned long *) 0xE0050024)) |

| #define | CAN4RDA (*((volatile unsigned long *) 0xE0050028)) |

| #define | CAN4RDB (*((volatile unsigned long *) 0xE005002C)) |

| #define | CAN4TFI1 (*((volatile unsigned long *) 0xE0050030)) |

| #define | CAN4TID1 (*((volatile unsigned long *) 0xE0050034)) |

| #define | CAN4TDA1 (*((volatile unsigned long *) 0xE0050038)) |

| #define | CAN4TDB1 (*((volatile unsigned long *) 0xE005003C)) |

| #define | CAN4TFI2 (*((volatile unsigned long *) 0xE0050040)) |

| #define | CAN4TID2 (*((volatile unsigned long *) 0xE0050044)) |

| #define | CAN4TDA2 (*((volatile unsigned long *) 0xE0050048)) |

| #define | CAN4TDB2 (*((volatile unsigned long *) 0xE005004C)) |

| #define | CAN4TFI3 (*((volatile unsigned long *) 0xE0050050)) |

| #define | CAN4TID3 (*((volatile unsigned long *) 0xE0050054)) |

| #define | CAN4TDA3 (*((volatile unsigned long *) 0xE0050058)) |

| #define | CAN4TDB3 (*((volatile unsigned long *) 0xE005005C)) |

| #define | CAN5MOD (*((volatile unsigned long *) 0xE0054000)) |

| #define | CAN5CMR (*((volatile unsigned long *) 0xE0054004)) |

| #define | CAN5GSR (*((volatile unsigned long *) 0xE0054008)) |

| #define | CAN5ICR (*((volatile unsigned long *) 0xE005400C)) |

| #define | CAN5IER (*((volatile unsigned long *) 0xE0054010)) |

| #define | CAN5BTR (*((volatile unsigned long *) 0xE0054014)) |

| #define | CAN5EWL (*((volatile unsigned long *) 0xE005401C)) |

| #define | CAN5SR (*((volatile unsigned long *) 0xE0054020)) |

| #define | CAN5RFS (*((volatile unsigned long *) 0xE0054024)) |

| #define | CAN5RDA (*((volatile unsigned long *) 0xE0054028)) |

| #define | CAN5RDB (*((volatile unsigned long *) 0xE005402C)) |

| #define | CAN5TFI1 (*((volatile unsigned long *) 0xE0054030)) |

| #define | CAN5TID1 (*((volatile unsigned long *) 0xE0054034)) |

| #define | CAN5TDA1 (*((volatile unsigned long *) 0xE0054038)) |

| #define | CAN5TDB1 (*((volatile unsigned long *) 0xE005403C)) |

| #define | CAN5TFI2 (*((volatile unsigned long *) 0xE0054040)) |

| #define | CAN5TID2 (*((volatile unsigned long *) 0xE0054044)) |

| #define | CAN5TDA2 (*((volatile unsigned long *) 0xE0054048)) |

| #define | CAN5TDB2 (*((volatile unsigned long *) 0xE005404C)) |

| #define | CAN5TFI3 (*((volatile unsigned long *) 0xE0054050)) |

| #define | CAN5TID3 (*((volatile unsigned long *) 0xE0054054)) |

| #define | CAN5TDA3 (*((volatile unsigned long *) 0xE0054058)) |

| #define | CAN5TDB3 (*((volatile unsigned long *) 0xE005405C)) |

| #define | CAN6MOD (*((volatile unsigned long *) 0xE0058000)) |

| #define | CAN6CMR (*((volatile unsigned long *) 0xE0058004)) |

| #define | CAN6GSR (*((volatile unsigned long *) 0xE0058008)) |

| #define | CAN6ICR (*((volatile unsigned long *) 0xE005800C)) |

| #define | CAN6IER (*((volatile unsigned long *) 0xE0058010)) |

| #define | CAN6BTR (*((volatile unsigned long *) 0xE0058014)) |

| #define | CAN6EWL (*((volatile unsigned long *) 0xE005801C)) |

| #define | CAN6SR (*((volatile unsigned long *) 0xE0058020)) |

| #define | CAN6RFS (*((volatile unsigned long *) 0xE0058024)) |

| #define | CAN6RDA (*((volatile unsigned long *) 0xE0058028)) |

| #define | CAN6RDB (*((volatile unsigned long *) 0xE005802C)) |

| #define | CAN6TFI1 (*((volatile unsigned long *) 0xE0058030)) |

| #define | CAN6TID1 (*((volatile unsigned long *) 0xE0058034)) |

| #define | CAN6TDA1 (*((volatile unsigned long *) 0xE0058038)) |

| #define | CAN6TDB1 (*((volatile unsigned long *) 0xE005803C)) |

| #define | CAN6TFI2 (*((volatile unsigned long *) 0xE0058040)) |

| #define | CAN6TID2 (*((volatile unsigned long *) 0xE0058044)) |

| #define | CAN6TDA2 (*((volatile unsigned long *) 0xE0058048)) |

| #define | CAN6TDB2 (*((volatile unsigned long *) 0xE005804C)) |

| #define | CAN6TFI3 (*((volatile unsigned long *) 0xE0058050)) |

| #define | CAN6TID3 (*((volatile unsigned long *) 0xE0058054)) |

| #define | CAN6TDA3 (*((volatile unsigned long *) 0xE0058058)) |

| #define | CAN6TDB3 (*((volatile unsigned long *) 0xE005805C)) |

| #define | CANTxSR (*((volatile unsigned long *) 0xE0040000)) |

| #define | CANRxSR (*((volatile unsigned long *) 0xE0040004)) |

| #define | CANMSR (*((volatile unsigned long *) 0xE0040008)) |

| #define | CANAFMR (*((volatile unsigned long *) 0xE003C000)) |

| #define | CANSFF_sa (*((volatile unsigned long *) 0xE003C004)) |

| #define | CANSFF_GRP_sa (*((volatile unsigned long *) 0xE003C008)) |

| #define | CANEFF_sa (*((volatile unsigned long *) 0xE003C00C)) |

| #define | CANEFF_GRP_sa (*((volatile unsigned long *) 0xE003C010)) |

| #define | CANENDofTable (*((volatile unsigned long *) 0xE003C014)) |

| #define | CANLUTerrAd (*((volatile unsigned long *) 0xE003C018)) |

| #define | CANLUTerr (*((volatile unsigned long *) 0xE003C01C)) |

| #define | CANAFRAM (*((volatile unsigned long *) 0xE0038000)) |

| #define | T0IR (*((volatile unsigned long *) 0xE0004000)) |

| #define | T0TCR (*((volatile unsigned long *) 0xE0004004)) |

| #define | T0TC (*((volatile unsigned long *) 0xE0004008)) |

| #define | T0PR (*((volatile unsigned long *) 0xE000400C)) |

| #define | T0PC (*((volatile unsigned long *) 0xE0004010)) |

| #define | T0MCR (*((volatile unsigned long *) 0xE0004014)) |

| #define | T0MR0 (*((volatile unsigned long *) 0xE0004018)) |

| #define | T0MR1 (*((volatile unsigned long *) 0xE000401C)) |

| #define | T0MR2 (*((volatile unsigned long *) 0xE0004020)) |

| #define | T0MR3 (*((volatile unsigned long *) 0xE0004024)) |

| #define | T0CCR (*((volatile unsigned long *) 0xE0004028)) |

| #define | T0CR0 (*((volatile unsigned long *) 0xE000402C)) |

| #define | T0CR1 (*((volatile unsigned long *) 0xE0004030)) |

| #define | T0CR2 (*((volatile unsigned long *) 0xE0004034)) |

| #define | T0CR3 (*((volatile unsigned long *) 0xE0004038)) |

| #define | T0EMR (*((volatile unsigned long *) 0xE000403C)) |

| #define | T0CTCR (*((volatile unsigned long *) 0xE0004070)) |

| #define | T1IR (*((volatile unsigned long *) 0xE0008000)) |

| #define | T1TCR (*((volatile unsigned long *) 0xE0008004)) |

| #define | T1TC (*((volatile unsigned long *) 0xE0008008)) |

| #define | T1PR (*((volatile unsigned long *) 0xE000800C)) |

| #define | T1PC (*((volatile unsigned long *) 0xE0008010)) |

| #define | T1MCR (*((volatile unsigned long *) 0xE0008014)) |

| #define | T1MR0 (*((volatile unsigned long *) 0xE0008018)) |

| #define | T1MR1 (*((volatile unsigned long *) 0xE000801C)) |

| #define | T1MR2 (*((volatile unsigned long *) 0xE0008020)) |

| #define | T1MR3 (*((volatile unsigned long *) 0xE0008024)) |

| #define | T1CCR (*((volatile unsigned long *) 0xE0008028)) |

| #define | T1CR0 (*((volatile unsigned long *) 0xE000802C)) |

| #define | T1CR1 (*((volatile unsigned long *) 0xE0008030)) |

| #define | T1CR2 (*((volatile unsigned long *) 0xE0008034)) |

| #define | T1CR3 (*((volatile unsigned long *) 0xE0008038)) |

| #define | T1EMR (*((volatile unsigned long *) 0xE000803C)) |

| #define | T1CTCR (*((volatile unsigned long *) 0xE0008070)) |

| #define | T2IR (*((volatile unsigned long *) 0xE0070000)) |

| #define | T2TCR (*((volatile unsigned long *) 0xE0070004)) |

| #define | T2TC (*((volatile unsigned long *) 0xE0070008)) |

| #define | T2PR (*((volatile unsigned long *) 0xE007000C)) |

| #define | T2PC (*((volatile unsigned long *) 0xE0070010)) |

| #define | T2MCR (*((volatile unsigned long *) 0xE0070014)) |

| #define | T2MR0 (*((volatile unsigned long *) 0xE0070018)) |

| #define | T2MR1 (*((volatile unsigned long *) 0xE007001C)) |

| #define | T2MR2 (*((volatile unsigned long *) 0xE0070020)) |

| #define | T2MR3 (*((volatile unsigned long *) 0xE0070024)) |

| #define | T2CCR (*((volatile unsigned long *) 0xE0070028)) |

| #define | T2CR0 (*((volatile unsigned long *) 0xE007002C)) |

| #define | T2CR1 (*((volatile unsigned long *) 0xE0070030)) |

| #define | T2CR2 (*((volatile unsigned long *) 0xE0070034)) |

| #define | T2CR3 (*((volatile unsigned long *) 0xE0070038)) |

| #define | T2EMR (*((volatile unsigned long *) 0xE007003C)) |

| #define | T2CTCR (*((volatile unsigned long *) 0xE0070070)) |

| #define | T3IR (*((volatile unsigned long *) 0xE0074000)) |

| #define | T3TCR (*((volatile unsigned long *) 0xE0074004)) |

| #define | T3TC (*((volatile unsigned long *) 0xE0074008)) |

| #define | T3PR (*((volatile unsigned long *) 0xE007400C)) |

| #define | T3PC (*((volatile unsigned long *) 0xE0074010)) |

| #define | T3MCR (*((volatile unsigned long *) 0xE0074014)) |

| #define | T3MR0 (*((volatile unsigned long *) 0xE0074018)) |

| #define | T3MR1 (*((volatile unsigned long *) 0xE007401C)) |

| #define | T3MR2 (*((volatile unsigned long *) 0xE0074020)) |

| #define | T3MR3 (*((volatile unsigned long *) 0xE0074024)) |

| #define | T3CCR (*((volatile unsigned long *) 0xE0074028)) |

| #define | T3CR0 (*((volatile unsigned long *) 0xE007402C)) |

| #define | T3CR1 (*((volatile unsigned long *) 0xE0074030)) |

| #define | T3CR2 (*((volatile unsigned long *) 0xE0074034)) |

| #define | T3CR3 (*((volatile unsigned long *) 0xE0074038)) |

| #define | T3EMR (*((volatile unsigned long *) 0xE007403C)) |

| #define | T3CTCR (*((volatile unsigned long *) 0xE0074070)) |

| #define | T0PWMCON (*((volatile unsigned long *) 0xE0004074)) |

| #define | T1PWMCON (*((volatile unsigned long *) 0xE0008074)) |

| #define | PWMIR (*((volatile unsigned long *) 0xE0014000)) |

| #define | PWMTCR (*((volatile unsigned long *) 0xE0014004)) |

| #define | PWMTC (*((volatile unsigned long *) 0xE0014008)) |

| #define | PWMPR (*((volatile unsigned long *) 0xE001400C)) |

| #define | PWMPC (*((volatile unsigned long *) 0xE0014010)) |

| #define | PWMMCR (*((volatile unsigned long *) 0xE0014014)) |

| #define | PWMMR0 (*((volatile unsigned long *) 0xE0014018)) |

| #define | PWMMR1 (*((volatile unsigned long *) 0xE001401C)) |

| #define | PWMMR2 (*((volatile unsigned long *) 0xE0014020)) |

| #define | PWMMR3 (*((volatile unsigned long *) 0xE0014024)) |

| #define | PWMMR4 (*((volatile unsigned long *) 0xE0014040)) |

| #define | PWMMR5 (*((volatile unsigned long *) 0xE0014044)) |

| #define | PWMMR6 (*((volatile unsigned long *) 0xE0014048)) |

| #define | PWMPCR (*((volatile unsigned long *) 0xE001404C)) |

| #define | PWMLER (*((volatile unsigned long *) 0xE0014050)) |

| #define | ADCR (*((volatile unsigned long *) 0xE0034000)) |

| #define | ADDR (*((volatile unsigned long *) 0xE0034004)) |

| #define | AD0CR (*((volatile unsigned long *) 0xE0034000)) |

| #define | AD0GDR (*((volatile unsigned long *) 0xE0034004)) |

| #define | AD0STAT (*((volatile unsigned long *) 0xE0034030)) |

| #define | AD0INTEN (*((volatile unsigned long *) 0xE003400C)) |

| #define | ILR (*((volatile unsigned char *) 0xE0024000)) |

| #define | CTC (*((volatile unsigned short*) 0xE0024004)) |

| #define | CCR (*((volatile unsigned char *) 0xE0024008)) |

| #define | CIIR (*((volatile unsigned char *) 0xE002400C)) |

| #define | AMR (*((volatile unsigned char *) 0xE0024010)) |

| #define | CTIME0 (*((volatile unsigned long *) 0xE0024014)) |

| #define | CTIME1 (*((volatile unsigned long *) 0xE0024018)) |

| #define | CTIME2 (*((volatile unsigned long *) 0xE002401C)) |

| #define | SEC (*((volatile unsigned char *) 0xE0024020)) |

| #define | MIN (*((volatile unsigned char *) 0xE0024024)) |

| #define | HOUR (*((volatile unsigned char *) 0xE0024028)) |

| #define | DOM (*((volatile unsigned char *) 0xE002402C)) |

| #define | DOW (*((volatile unsigned char *) 0xE0024030)) |

| #define | DOY (*((volatile unsigned short*) 0xE0024034)) |

| #define | MONTH (*((volatile unsigned char *) 0xE0024038)) |

| #define | YEAR (*((volatile unsigned short*) 0xE002403C)) |

| #define | ALSEC (*((volatile unsigned char *) 0xE0024060)) |

| #define | ALMIN (*((volatile unsigned char *) 0xE0024064)) |

| #define | ALHOUR (*((volatile unsigned char *) 0xE0024068)) |

| #define | ALDOM (*((volatile unsigned char *) 0xE002406C)) |

| #define | ALDOW (*((volatile unsigned char *) 0xE0024070)) |

| #define | ALDOY (*((volatile unsigned short*) 0xE0024074)) |

| #define | ALMON (*((volatile unsigned char *) 0xE0024078)) |

| #define | ALYEAR (*((volatile unsigned short*) 0xE002407C)) |

| #define | PREINT (*((volatile unsigned short*) 0xE0024080)) |

| #define | PREFRAC (*((volatile unsigned short*) 0xE0024084)) |

| #define | WDMOD (*((volatile unsigned char *) 0xE0000000)) |

| #define | WDTC (*((volatile unsigned long *) 0xE0000004)) |

| #define | WDFEED (*((volatile unsigned char *) 0xE0000008)) |

| #define | WDTV (*((volatile unsigned long *) 0xE000000C)) |

| #define | WDFLAG (*((volatile unsigned long *) 0xE01FC180)) |

| #define | rm_init_entry() ((void (*)())(0x7fffff91))() |

| #define | rm_undef_handler() ((void (*)())(0x7fffffa0))() |

| #define | rm_prefetchabort_handler() ((void (*)())(0x7fffffb0))() |

| #define | rm_dataabort_handler() ((void (*)())(0x7fffffc0))() |

| #define | rm_irqhandler() ((void (*)())(0x7fffffd0))() |

| #define | rm_irqhandler2() ((void (*)())(0x7fffffe0))() |

| #define | iap_entry(a, b) ((void (*)())(0x7ffffff1))(a, b) |

Define Documentation

| #define AD0CR (*((volatile unsigned long *) 0xE0034000)) |

Referenced by ADC_Init().

| #define AD0GDR (*((volatile unsigned long *) 0xE0034004)) |

Referenced by adcISR0().

| #define AD0INTEN (*((volatile unsigned long *) 0xE003400C)) |

| #define AD0STAT (*((volatile unsigned long *) 0xE0034030)) |

| #define ADCR (*((volatile unsigned long *) 0xE0034000)) |

| #define ADDR (*((volatile unsigned long *) 0xE0034004)) |

| #define ALDOM (*((volatile unsigned char *) 0xE002406C)) |

| #define ALDOW (*((volatile unsigned char *) 0xE0024070)) |

| #define ALDOY (*((volatile unsigned short*) 0xE0024074)) |

| #define ALHOUR (*((volatile unsigned char *) 0xE0024068)) |

| #define ALMIN (*((volatile unsigned char *) 0xE0024064)) |

| #define ALMON (*((volatile unsigned char *) 0xE0024078)) |

| #define ALSEC (*((volatile unsigned char *) 0xE0024060)) |

| #define ALYEAR (*((volatile unsigned short*) 0xE002407C)) |

| #define AMR (*((volatile unsigned char *) 0xE0024010)) |

| #define APBDIV (*((volatile unsigned char *) 0xE01FC100)) |

Referenced by GPIOInit(), and UARTInit().

| #define BCFG0 (*((volatile unsigned int *) 0xFFE00000)) |

| #define BCFG1 (*((volatile unsigned int *) 0xFFE00004)) |

| #define BCFG2 (*((volatile unsigned int *) 0xFFE00008)) |

| #define BCFG3 (*((volatile unsigned int *) 0xFFE0000C)) |

| #define CAN1BTR (*((volatile unsigned long *) 0xE0044014)) |

| #define CAN1CMR (*((volatile unsigned long *) 0xE0044004)) |

| #define CAN1EWL (*((volatile unsigned long *) 0xE004401C)) |

| #define CAN1GSR (*((volatile unsigned long *) 0xE0044008)) |

| #define CAN1ICR (*((volatile unsigned long *) 0xE004400C)) |

| #define CAN1IER (*((volatile unsigned long *) 0xE0044010)) |

| #define CAN1MOD (*((volatile unsigned long *) 0xE0044000)) |

| #define CAN1RDA (*((volatile unsigned long *) 0xE0044028)) |

| #define CAN1RDB (*((volatile unsigned long *) 0xE004402C)) |

| #define CAN1RFS (*((volatile unsigned long *) 0xE0044024)) |

| #define CAN1SR (*((volatile unsigned long *) 0xE0044020)) |

| #define CAN1TDA1 (*((volatile unsigned long *) 0xE0044038)) |

| #define CAN1TDA2 (*((volatile unsigned long *) 0xE0044048)) |

| #define CAN1TDA3 (*((volatile unsigned long *) 0xE0044058)) |

| #define CAN1TDB1 (*((volatile unsigned long *) 0xE004403C)) |

| #define CAN1TDB2 (*((volatile unsigned long *) 0xE004404C)) |

| #define CAN1TDB3 (*((volatile unsigned long *) 0xE004405C)) |

| #define CAN1TFI1 (*((volatile unsigned long *) 0xE0044030)) |

| #define CAN1TFI2 (*((volatile unsigned long *) 0xE0044040)) |

| #define CAN1TFI3 (*((volatile unsigned long *) 0xE0044050)) |

| #define CAN1TID1 (*((volatile unsigned long *) 0xE0044034)) |

| #define CAN1TID2 (*((volatile unsigned long *) 0xE0044044)) |

| #define CAN1TID3 (*((volatile unsigned long *) 0xE0044054)) |

| #define CAN2BTR (*((volatile unsigned long *) 0xE0048014)) |

| #define CAN2CMR (*((volatile unsigned long *) 0xE0048004)) |

| #define CAN2EWL (*((volatile unsigned long *) 0xE004801C)) |

| #define CAN2GSR (*((volatile unsigned long *) 0xE0048008)) |

| #define CAN2ICR (*((volatile unsigned long *) 0xE004800C)) |

| #define CAN2IER (*((volatile unsigned long *) 0xE0048010)) |

| #define CAN2MOD (*((volatile unsigned long *) 0xE0048000)) |

| #define CAN2RDA (*((volatile unsigned long *) 0xE0048028)) |

| #define CAN2RDB (*((volatile unsigned long *) 0xE004802C)) |

| #define CAN2RFS (*((volatile unsigned long *) 0xE0048024)) |

| #define CAN2SR (*((volatile unsigned long *) 0xE0048020)) |

| #define CAN2TDA1 (*((volatile unsigned long *) 0xE0048038)) |

| #define CAN2TDA2 (*((volatile unsigned long *) 0xE0048048)) |

| #define CAN2TDA3 (*((volatile unsigned long *) 0xE0048058)) |

| #define CAN2TDB1 (*((volatile unsigned long *) 0xE004803C)) |

| #define CAN2TDB2 (*((volatile unsigned long *) 0xE004804C)) |

| #define CAN2TDB3 (*((volatile unsigned long *) 0xE004805C)) |

| #define CAN2TFI1 (*((volatile unsigned long *) 0xE0048030)) |

| #define CAN2TFI2 (*((volatile unsigned long *) 0xE0048040)) |

| #define CAN2TFI3 (*((volatile unsigned long *) 0xE0048050)) |

| #define CAN2TID1 (*((volatile unsigned long *) 0xE0048034)) |

| #define CAN2TID2 (*((volatile unsigned long *) 0xE0048044)) |

| #define CAN2TID3 (*((volatile unsigned long *) 0xE0048054)) |

| #define CAN3BTR (*((volatile unsigned long *) 0xE004C014)) |

| #define CAN3CMR (*((volatile unsigned long *) 0xE004C004)) |

| #define CAN3EWL (*((volatile unsigned long *) 0xE004C01C)) |

| #define CAN3GSR (*((volatile unsigned long *) 0xE004C008)) |

| #define CAN3ICR (*((volatile unsigned long *) 0xE004C00C)) |

| #define CAN3IER (*((volatile unsigned long *) 0xE004C010)) |

| #define CAN3MOD (*((volatile unsigned long *) 0xE004C000)) |

| #define CAN3RDA (*((volatile unsigned long *) 0xE004C028)) |

| #define CAN3RDB (*((volatile unsigned long *) 0xE004C02C)) |

| #define CAN3RFS (*((volatile unsigned long *) 0xE004C024)) |

| #define CAN3SR (*((volatile unsigned long *) 0xE004C020)) |

| #define CAN3TDA1 (*((volatile unsigned long *) 0xE004C038)) |

| #define CAN3TDA2 (*((volatile unsigned long *) 0xE004C048)) |

| #define CAN3TDA3 (*((volatile unsigned long *) 0xE004C058)) |

| #define CAN3TDB1 (*((volatile unsigned long *) 0xE004C03C)) |

| #define CAN3TDB2 (*((volatile unsigned long *) 0xE004C04C)) |

| #define CAN3TDB3 (*((volatile unsigned long *) 0xE004C05C)) |

| #define CAN3TFI1 (*((volatile unsigned long *) 0xE004C030)) |

| #define CAN3TFI2 (*((volatile unsigned long *) 0xE004C040)) |

| #define CAN3TFI3 (*((volatile unsigned long *) 0xE004C050)) |

| #define CAN3TID1 (*((volatile unsigned long *) 0xE004C034)) |

| #define CAN3TID2 (*((volatile unsigned long *) 0xE004C044)) |

| #define CAN3TID3 (*((volatile unsigned long *) 0xE004C054)) |

| #define CAN4BTR (*((volatile unsigned long *) 0xE0050014)) |

| #define CAN4CMR (*((volatile unsigned long *) 0xE0050004)) |

| #define CAN4EWL (*((volatile unsigned long *) 0xE005001C)) |

| #define CAN4GSR (*((volatile unsigned long *) 0xE0050008)) |

| #define CAN4ICR (*((volatile unsigned long *) 0xE005000C)) |

| #define CAN4IER (*((volatile unsigned long *) 0xE0050010)) |

| #define CAN4MOD (*((volatile unsigned long *) 0xE0050000)) |

| #define CAN4RDA (*((volatile unsigned long *) 0xE0050028)) |

| #define CAN4RDB (*((volatile unsigned long *) 0xE005002C)) |

| #define CAN4RFS (*((volatile unsigned long *) 0xE0050024)) |

| #define CAN4SR (*((volatile unsigned long *) 0xE0050020)) |

| #define CAN4TDA1 (*((volatile unsigned long *) 0xE0050038)) |

| #define CAN4TDA2 (*((volatile unsigned long *) 0xE0050048)) |

| #define CAN4TDA3 (*((volatile unsigned long *) 0xE0050058)) |

| #define CAN4TDB1 (*((volatile unsigned long *) 0xE005003C)) |

| #define CAN4TDB2 (*((volatile unsigned long *) 0xE005004C)) |

| #define CAN4TDB3 (*((volatile unsigned long *) 0xE005005C)) |

| #define CAN4TFI1 (*((volatile unsigned long *) 0xE0050030)) |

| #define CAN4TFI2 (*((volatile unsigned long *) 0xE0050040)) |

| #define CAN4TFI3 (*((volatile unsigned long *) 0xE0050050)) |

| #define CAN4TID1 (*((volatile unsigned long *) 0xE0050034)) |

| #define CAN4TID2 (*((volatile unsigned long *) 0xE0050044)) |

| #define CAN4TID3 (*((volatile unsigned long *) 0xE0050054)) |

| #define CAN5BTR (*((volatile unsigned long *) 0xE0054014)) |

| #define CAN5CMR (*((volatile unsigned long *) 0xE0054004)) |

| #define CAN5EWL (*((volatile unsigned long *) 0xE005401C)) |

| #define CAN5GSR (*((volatile unsigned long *) 0xE0054008)) |

| #define CAN5ICR (*((volatile unsigned long *) 0xE005400C)) |

| #define CAN5IER (*((volatile unsigned long *) 0xE0054010)) |

| #define CAN5MOD (*((volatile unsigned long *) 0xE0054000)) |

| #define CAN5RDA (*((volatile unsigned long *) 0xE0054028)) |

| #define CAN5RDB (*((volatile unsigned long *) 0xE005402C)) |

| #define CAN5RFS (*((volatile unsigned long *) 0xE0054024)) |

| #define CAN5SR (*((volatile unsigned long *) 0xE0054020)) |

| #define CAN5TDA1 (*((volatile unsigned long *) 0xE0054038)) |

| #define CAN5TDA2 (*((volatile unsigned long *) 0xE0054048)) |

| #define CAN5TDA3 (*((volatile unsigned long *) 0xE0054058)) |

| #define CAN5TDB1 (*((volatile unsigned long *) 0xE005403C)) |

| #define CAN5TDB2 (*((volatile unsigned long *) 0xE005404C)) |

| #define CAN5TDB3 (*((volatile unsigned long *) 0xE005405C)) |

| #define CAN5TFI1 (*((volatile unsigned long *) 0xE0054030)) |

| #define CAN5TFI2 (*((volatile unsigned long *) 0xE0054040)) |

| #define CAN5TFI3 (*((volatile unsigned long *) 0xE0054050)) |

| #define CAN5TID1 (*((volatile unsigned long *) 0xE0054034)) |

| #define CAN5TID2 (*((volatile unsigned long *) 0xE0054044)) |

| #define CAN5TID3 (*((volatile unsigned long *) 0xE0054054)) |

| #define CAN6BTR (*((volatile unsigned long *) 0xE0058014)) |

| #define CAN6CMR (*((volatile unsigned long *) 0xE0058004)) |

| #define CAN6EWL (*((volatile unsigned long *) 0xE005801C)) |

| #define CAN6GSR (*((volatile unsigned long *) 0xE0058008)) |

| #define CAN6ICR (*((volatile unsigned long *) 0xE005800C)) |

| #define CAN6IER (*((volatile unsigned long *) 0xE0058010)) |

| #define CAN6MOD (*((volatile unsigned long *) 0xE0058000)) |

| #define CAN6RDA (*((volatile unsigned long *) 0xE0058028)) |

| #define CAN6RDB (*((volatile unsigned long *) 0xE005802C)) |

| #define CAN6RFS (*((volatile unsigned long *) 0xE0058024)) |

| #define CAN6SR (*((volatile unsigned long *) 0xE0058020)) |

| #define CAN6TDA1 (*((volatile unsigned long *) 0xE0058038)) |

| #define CAN6TDA2 (*((volatile unsigned long *) 0xE0058048)) |

| #define CAN6TDA3 (*((volatile unsigned long *) 0xE0058058)) |

| #define CAN6TDB1 (*((volatile unsigned long *) 0xE005803C)) |

| #define CAN6TDB2 (*((volatile unsigned long *) 0xE005804C)) |

| #define CAN6TDB3 (*((volatile unsigned long *) 0xE005805C)) |

| #define CAN6TFI1 (*((volatile unsigned long *) 0xE0058030)) |

| #define CAN6TFI2 (*((volatile unsigned long *) 0xE0058040)) |

| #define CAN6TFI3 (*((volatile unsigned long *) 0xE0058050)) |

| #define CAN6TID1 (*((volatile unsigned long *) 0xE0058034)) |

| #define CAN6TID2 (*((volatile unsigned long *) 0xE0058044)) |

| #define CAN6TID3 (*((volatile unsigned long *) 0xE0058054)) |

| #define CANAFMR (*((volatile unsigned long *) 0xE003C000)) |

| #define CANAFRAM (*((volatile unsigned long *) 0xE0038000)) |

| #define CANEFF_GRP_sa (*((volatile unsigned long *) 0xE003C010)) |

| #define CANEFF_sa (*((volatile unsigned long *) 0xE003C00C)) |

| #define CANENDofTable (*((volatile unsigned long *) 0xE003C014)) |

| #define CANLUTerr (*((volatile unsigned long *) 0xE003C01C)) |

| #define CANLUTerrAd (*((volatile unsigned long *) 0xE003C018)) |

| #define CANMSR (*((volatile unsigned long *) 0xE0040008)) |

| #define CANRxSR (*((volatile unsigned long *) 0xE0040004)) |

| #define CANSFF_GRP_sa (*((volatile unsigned long *) 0xE003C008)) |

| #define CANSFF_sa (*((volatile unsigned long *) 0xE003C004)) |

| #define CANTxSR (*((volatile unsigned long *) 0xE0040000)) |

| #define CCR (*((volatile unsigned char *) 0xE0024008)) |

| #define CIIR (*((volatile unsigned char *) 0xE002400C)) |

| #define CTC (*((volatile unsigned short*) 0xE0024004)) |

| #define CTIME0 (*((volatile unsigned long *) 0xE0024014)) |

| #define CTIME1 (*((volatile unsigned long *) 0xE0024018)) |

| #define CTIME2 (*((volatile unsigned long *) 0xE002401C)) |

| #define DOM (*((volatile unsigned char *) 0xE002402C)) |

| #define DOW (*((volatile unsigned char *) 0xE0024030)) |

| #define DOY (*((volatile unsigned short*) 0xE0024034)) |

| #define EXTINT (*((volatile unsigned char *) 0xE01FC140)) |

| #define EXTMODE (*((volatile unsigned char *) 0xE01FC148)) |

| #define EXTPOLAR (*((volatile unsigned char *) 0xE01FC14C)) |

| #define EXTWAKE (*((volatile unsigned char *) 0xE01FC144)) |

| #define FIOCLR (*((volatile unsigned long *) 0x3FFFC01C)) |

Referenced by EnterISPMode(), GPIOInit(), and main().

| #define FIOMASK (*((volatile unsigned long *) 0x3FFFC010)) |

| #define FIOPIN (*((volatile unsigned long *) 0x3FFFC014)) |

Referenced by GPIOInit().

| #define FIOSET (*((volatile unsigned long *) 0x3FFFC018)) |

Referenced by EnterISPMode(), GPIOInit(), main(), and SSD1928Init().

| #define HOUR (*((volatile unsigned char *) 0xE0024028)) |

| #define I2AA 0x04 |

| #define I2ADR (*((volatile unsigned char *) 0xE001C00C)) |

| #define I2CONCLR (*((volatile unsigned char *) 0xE001C018)) |

| #define I2CONSET (*((volatile unsigned char *) 0xE001C000)) |

| #define I2DAT (*((volatile unsigned char *) 0xE001C008)) |

| #define I2EN 0x40 |

| #define I2SCLH (*((volatile unsigned short *) 0xE001C010)) |

| #define I2SCLL (*((volatile unsigned short *) 0xE001C014)) |

| #define I2SI 0x08 |

| #define I2STA 0x20 |

| #define I2STAT (*((volatile unsigned char *) 0xE001C004)) |

| #define I2STO 0x10 |

| #define iap_entry | ( | a, | |||

| b | ) | ((void (*)())(0x7ffffff1))(a, b) |

| #define ILR (*((volatile unsigned char *) 0xE0024000)) |

| #define IO0CLR (*((volatile unsigned long *) 0xE002800C)) |

| #define IO0DIR (*((volatile unsigned long *) 0xE0028008)) |

| #define IO0PIN (*((volatile unsigned long *) 0xE0028000)) |

| #define IO0SET (*((volatile unsigned long *) 0xE0028004)) |

| #define IO1CLR (*((volatile unsigned long *) 0xE002801C)) |

| #define IO1DIR (*((volatile unsigned long *) 0xE0028018)) |

| #define IO1PIN (*((volatile unsigned long *) 0xE0028010)) |

| #define IO1SET (*((volatile unsigned long *) 0xE0028014)) |

| #define IO2CLR (*((volatile unsigned long *) 0xE002802C)) |

| #define IO2DIR (*((volatile unsigned long *) 0xE0028028)) |

| #define IO2PIN (*((volatile unsigned long *) 0xE0028020)) |

| #define IO2SET (*((volatile unsigned long *) 0xE0028024)) |

| #define IO3CLR (*((volatile unsigned long *) 0xE002803C)) |

| #define IO3DIR (*((volatile unsigned long *) 0xE0028038)) |

| #define IO3PIN (*((volatile unsigned long *) 0xE0028030)) |

| #define IO3SET (*((volatile unsigned long *) 0xE0028034)) |

| #define IOCLR (*((volatile unsigned long *) 0xE002800C)) |

| #define IODIR (*((volatile unsigned long *) 0xE0028008)) |

| #define IOPIN (*((volatile unsigned long *) 0xE0028000)) |

| #define IOSET (*((volatile unsigned long *) 0xE0028004)) |

| #define LPC210X_FAST_GPIO |

| #define MAMCR (*((volatile unsigned char *) 0xE01FC000)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define MAMTIM (*((volatile unsigned char *) 0xE01FC004)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define MEMMAP (*((volatile unsigned char *) 0xE01FC040)) |

Referenced by EnterISPMode().

| #define MIN (*((volatile unsigned char *) 0xE0024024)) |

| #define MONTH (*((volatile unsigned char *) 0xE0024038)) |

| #define PCON (*((volatile unsigned char *) 0xE01FC0C0)) |

| #define PCONP (*((volatile unsigned long *) 0xE01FC0C4)) |

Referenced by timer2_init().

| #define PINSEL0 (*((volatile unsigned long *) 0xE002C000)) |

Referenced by DisableUART(), EnterISPMode(), GPIOInit(), init_I2C(), and InitUART().

| #define PINSEL1 (*((volatile unsigned long *) 0xE002C004)) |

Referenced by ADC_Init(), EnterISPMode(), GPIOInit(), init_I2C(), timer2_done(), timer2_init(), and TP_Init().

| #define PINSEL2 (*((volatile unsigned long *) 0xE002C014)) |

| #define PLLCFG (*((volatile unsigned char *) 0xE01FC084)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define PLLCON (*((volatile unsigned char *) 0xE01FC080)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define PLLFEED (*((volatile unsigned char *) 0xE01FC08C)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define PLLSTAT (*((volatile unsigned short*) 0xE01FC088)) |

Referenced by GPIOInit().

| #define PREFRAC (*((volatile unsigned short*) 0xE0024084)) |

| #define PREINT (*((volatile unsigned short*) 0xE0024080)) |

| #define PWMIR (*((volatile unsigned long *) 0xE0014000)) |

| #define PWMLER (*((volatile unsigned long *) 0xE0014050)) |

| #define PWMMCR (*((volatile unsigned long *) 0xE0014014)) |

| #define PWMMR0 (*((volatile unsigned long *) 0xE0014018)) |

| #define PWMMR1 (*((volatile unsigned long *) 0xE001401C)) |

| #define PWMMR2 (*((volatile unsigned long *) 0xE0014020)) |

| #define PWMMR3 (*((volatile unsigned long *) 0xE0014024)) |

| #define PWMMR4 (*((volatile unsigned long *) 0xE0014040)) |

| #define PWMMR5 (*((volatile unsigned long *) 0xE0014044)) |

| #define PWMMR6 (*((volatile unsigned long *) 0xE0014048)) |

| #define PWMPC (*((volatile unsigned long *) 0xE0014010)) |

| #define PWMPCR (*((volatile unsigned long *) 0xE001404C)) |

| #define PWMPR (*((volatile unsigned long *) 0xE001400C)) |

| #define PWMTC (*((volatile unsigned long *) 0xE0014008)) |

| #define PWMTCR (*((volatile unsigned long *) 0xE0014004)) |

| #define rm_dataabort_handler | ( | ) | ((void (*)())(0x7fffffc0))() |

| #define rm_init_entry | ( | ) | ((void (*)())(0x7fffff91))() |

| #define rm_irqhandler | ( | ) | ((void (*)())(0x7fffffd0))() |

| #define rm_irqhandler2 | ( | ) | ((void (*)())(0x7fffffe0))() |

| #define rm_prefetchabort_handler | ( | ) | ((void (*)())(0x7fffffb0))() |

| #define rm_undef_handler | ( | ) | ((void (*)())(0x7fffffa0))() |

| #define S0PCCR (*((volatile unsigned char *) 0xE002000C)) |

| #define S0PCR (*((volatile unsigned char *) 0xE0020000)) |

| #define S0PDR (*((volatile unsigned char *) 0xE0020008)) |

| #define S0PINT (*((volatile unsigned char *) 0xE002001C)) |

| #define S0PSR (*((volatile unsigned char *) 0xE0020004)) |

| #define S1PCCR (*((volatile unsigned char *) 0xE003000C)) |

| #define S1PCR (*((volatile unsigned char *) 0xE0030000)) |

| #define S1PDR (*((volatile unsigned char *) 0xE0030008)) |

| #define S1PINT (*((volatile unsigned char *) 0xE003001C)) |

| #define S1PSR (*((volatile unsigned char *) 0xE0030004)) |

| #define SEC (*((volatile unsigned char *) 0xE0024020)) |

| #define SPI_SPCCR (*((volatile unsigned char *) 0xE002000C)) |

| #define SPI_SPCR (*((volatile unsigned char *) 0xE0020000)) |

| #define SPI_SPDR (*((volatile unsigned char *) 0xE0020008)) |

| #define SPI_SPINT (*((volatile unsigned char *) 0xE002001C)) |

| #define SPI_SPSR (*((volatile unsigned char *) 0xE0020004)) |

| #define T0CCR (*((volatile unsigned long *) 0xE0004028)) |

Referenced by EnterISPMode().

| #define T0CR0 (*((volatile unsigned long *) 0xE000402C)) |

| #define T0CR1 (*((volatile unsigned long *) 0xE0004030)) |

| #define T0CR2 (*((volatile unsigned long *) 0xE0004034)) |

| #define T0CR3 (*((volatile unsigned long *) 0xE0004038)) |

| #define T0CTCR (*((volatile unsigned long *) 0xE0004070)) |

Referenced by timer_init().

| #define T0EMR (*((volatile unsigned long *) 0xE000403C)) |

Referenced by EnterISPMode().

| #define T0IR (*((volatile unsigned long *) 0xE0004000)) |

Referenced by timer_ISR().

| #define T0MCR (*((volatile unsigned long *) 0xE0004014)) |

Referenced by EnterISPMode(), and timer_init().

| #define T0MR0 (*((volatile unsigned long *) 0xE0004018)) |

Referenced by timer_init().

| #define T0MR1 (*((volatile unsigned long *) 0xE000401C)) |

| #define T0MR2 (*((volatile unsigned long *) 0xE0004020)) |

| #define T0MR3 (*((volatile unsigned long *) 0xE0004024)) |

| #define T0PC (*((volatile unsigned long *) 0xE0004010)) |

| #define T0PR (*((volatile unsigned long *) 0xE000400C)) |

Referenced by EnterISPMode().

| #define T0PWMCON (*((volatile unsigned long *) 0xE0004074)) |

Referenced by EnterISPMode().

| #define T0TC (*((volatile unsigned long *) 0xE0004008)) |

Referenced by EnterISPMode().

| #define T0TCR (*((volatile unsigned long *) 0xE0004004)) |

Referenced by EnterISPMode(), and timer_init().

| #define T1CCR (*((volatile unsigned long *) 0xE0008028)) |

Referenced by EnterISPMode().

| #define T1CR0 (*((volatile unsigned long *) 0xE000802C)) |

| #define T1CR1 (*((volatile unsigned long *) 0xE0008030)) |

| #define T1CR2 (*((volatile unsigned long *) 0xE0008034)) |

| #define T1CR3 (*((volatile unsigned long *) 0xE0008038)) |

| #define T1CTCR (*((volatile unsigned long *) 0xE0008070)) |

| #define T1EMR (*((volatile unsigned long *) 0xE000803C)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define T1IR (*((volatile unsigned long *) 0xE0008000)) |

| #define T1MCR (*((volatile unsigned long *) 0xE0008014)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define T1MR0 (*((volatile unsigned long *) 0xE0008018)) |

| #define T1MR1 (*((volatile unsigned long *) 0xE000801C)) |

Referenced by GPIOInit().

| #define T1MR2 (*((volatile unsigned long *) 0xE0008020)) |

Referenced by GPIOInit().

| #define T1MR3 (*((volatile unsigned long *) 0xE0008024)) |

Referenced by GPIOInit().

| #define T1PC (*((volatile unsigned long *) 0xE0008010)) |

| #define T1PR (*((volatile unsigned long *) 0xE000800C)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define T1PWMCON (*((volatile unsigned long *) 0xE0008074)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define T1TC (*((volatile unsigned long *) 0xE0008008)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define T1TCR (*((volatile unsigned long *) 0xE0008004)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define T2CCR (*((volatile unsigned long *) 0xE0070028)) |

Referenced by timer2_init().

| #define T2CR0 (*((volatile unsigned long *) 0xE007002C)) |

| #define T2CR1 (*((volatile unsigned long *) 0xE0070030)) |

| #define T2CR2 (*((volatile unsigned long *) 0xE0070034)) |

| #define T2CR3 (*((volatile unsigned long *) 0xE0070038)) |

| #define T2CTCR (*((volatile unsigned long *) 0xE0070070)) |

Referenced by timer2_init().

| #define T2EMR (*((volatile unsigned long *) 0xE007003C)) |

| #define T2IR (*((volatile unsigned long *) 0xE0070000)) |

Referenced by timer2_ISR().

| #define T2MCR (*((volatile unsigned long *) 0xE0070014)) |

Referenced by timer2_init().

| #define T2MR0 (*((volatile unsigned long *) 0xE0070018)) |

Referenced by timer2_init().

| #define T2MR1 (*((volatile unsigned long *) 0xE007001C)) |

| #define T2MR2 (*((volatile unsigned long *) 0xE0070020)) |

| #define T2MR3 (*((volatile unsigned long *) 0xE0070024)) |

| #define T2PC (*((volatile unsigned long *) 0xE0070010)) |

| #define T2PR (*((volatile unsigned long *) 0xE007000C)) |

| #define T2TC (*((volatile unsigned long *) 0xE0070008)) |

Referenced by timer2_init().

| #define T2TCR (*((volatile unsigned long *) 0xE0070004)) |

Referenced by timer2_done(), timer2_init(), and timer2_ISR().

| #define T3CCR (*((volatile unsigned long *) 0xE0074028)) |

| #define T3CR0 (*((volatile unsigned long *) 0xE007402C)) |

| #define T3CR1 (*((volatile unsigned long *) 0xE0074030)) |

| #define T3CR2 (*((volatile unsigned long *) 0xE0074034)) |

| #define T3CR3 (*((volatile unsigned long *) 0xE0074038)) |

| #define T3CTCR (*((volatile unsigned long *) 0xE0074070)) |

| #define T3EMR (*((volatile unsigned long *) 0xE007403C)) |

| #define T3IR (*((volatile unsigned long *) 0xE0074000)) |

| #define T3MCR (*((volatile unsigned long *) 0xE0074014)) |

| #define T3MR0 (*((volatile unsigned long *) 0xE0074018)) |

| #define T3MR1 (*((volatile unsigned long *) 0xE007401C)) |

| #define T3MR2 (*((volatile unsigned long *) 0xE0074020)) |

| #define T3MR3 (*((volatile unsigned long *) 0xE0074024)) |

| #define T3PC (*((volatile unsigned long *) 0xE0074010)) |

| #define T3PR (*((volatile unsigned long *) 0xE007400C)) |

| #define T3TC (*((volatile unsigned long *) 0xE0074008)) |

| #define T3TCR (*((volatile unsigned long *) 0xE0074004)) |

| #define U0ACR (*((volatile unsigned char *) 0xE000C020)) |

| #define U0DLL (*((volatile unsigned char *) 0xE000C000)) |

Referenced by EnterISPMode(), and InitUART().

| #define U0DLM (*((volatile unsigned char *) 0xE000C004)) |

Referenced by EnterISPMode(), and InitUART().

| #define U0FCR (*((volatile unsigned char *) 0xE000C008)) |

Referenced by EnterISPMode(), and InitUART().

| #define U0FDR (*((volatile unsigned char *) 0xE000C028)) |

Referenced by EnterISPMode(), and InitUART().

| #define U0IER (*((volatile unsigned char *) 0xE000C004)) |

Referenced by uart0_init_IRQ(), and uart0_transmit().

| #define U0IIR (*((volatile unsigned char *) 0xE000C008)) |

Referenced by uart0_ISR().

| #define U0LCR (*((volatile unsigned char *) 0xE000C00C)) |

Referenced by EnterISPMode(), and InitUART().

| #define U0LSR (*((volatile unsigned char *) 0xE000C014)) |

Referenced by ProcessUartIo(), uart0_ISR(), uart0_transmit(), UART_SendChar(), and UARTReceiveSingleTextLine().

| #define U0RBR (*((volatile unsigned char *) 0xE000C000)) |

Referenced by ProcessUartIo(), uart0_ISR(), and UARTReceiveSingleTextLine().

| #define U0SCR (*((volatile unsigned char *) 0xE000C01C)) |

| #define U0TER (*((volatile unsigned char *) 0xE000C030)) |

Referenced by EnterISPMode().

| #define U0THR (*((volatile unsigned char *) 0xE000C000)) |

Referenced by uart0_ISR(), uart0_transmit(), UART_SendChar(), and UARTReceiveSingleTextLine().

| #define U1DLL (*((volatile unsigned char *) 0xE0010000)) |

| #define U1DLM (*((volatile unsigned char *) 0xE0010004)) |

| #define U1FCR (*((volatile unsigned char *) 0xE0010008)) |

| #define U1IER (*((volatile unsigned char *) 0xE0010004)) |

| #define U1IIR (*((volatile unsigned char *) 0xE0010008)) |

| #define U1LCR (*((volatile unsigned char *) 0xE001000C)) |

| #define U1LSR (*((volatile unsigned char *) 0xE0010014)) |

| #define U1MCR (*((volatile unsigned char *) 0xE0010010)) |

| #define U1MSR (*((volatile unsigned char *) 0xE0010018)) |

| #define U1RBR (*((volatile unsigned char *) 0xE0010000)) |

| #define U1SCR (*((volatile unsigned char *) 0xE001001C)) |

| #define U1THR (*((volatile unsigned char *) 0xE0010000)) |

| #define UFCR_FIFO_ENABLE (1 << 0) |

| #define UFCR_FIFO_TRIG1 (0 << 6) |

| #define UFCR_FIFO_TRIG14 (3 << 6) |

| #define UFCR_FIFO_TRIG4 (1 << 6) |

| #define UFCR_FIFO_TRIG8 (2 << 6) |

| #define UFCR_RX_FIFO_RESET (1 << 1) |

| #define UFCR_TX_FIFO_RESET (1 << 2) |

| #define UIER_EDSSI (1 << 3) |

| #define UIER_ELSI (1 << 2) |

| #define UIER_ERBFI (1 << 0) |

Referenced by uart0_init_IRQ().

| #define UIER_ETBEI (1 << 1) |

Referenced by uart0_transmit().

| #define UIIR_CTI_INT (6 << 1) |

Referenced by uart0_ISR().

| #define UIIR_ID_MASK 0x0E |

Referenced by uart0_ISR().

| #define UIIR_MS_INT (0 << 1) |

| #define UIIR_NO_INT (1 << 0) |

Referenced by uart0_ISR().

| #define UIIR_RDA_INT (2 << 1) |

Referenced by uart0_ISR().

| #define UIIR_RLS_INT (3 << 1) |

Referenced by uart0_ISR().

| #define UIIR_THRE_INT (1 << 1) |

Referenced by uart0_ISR().

| #define ULCR_BREAK_ENABLE (1 << 6) |

| #define ULCR_CHAR_5 (0 << 0) |

| #define ULCR_CHAR_6 (1 << 0) |

| #define ULCR_CHAR_7 (2 << 0) |

| #define ULCR_CHAR_8 (3 << 0) |

| #define ULCR_DLAB_ENABLE (1 << 7) |

| #define ULCR_PAR_EVEN (3 << 3) |

| #define ULCR_PAR_MARK (5 << 3) |

| #define ULCR_PAR_NO (0 << 3) |

| #define ULCR_PAR_ODD (1 << 3) |

| #define ULCR_PAR_SPACE (7 << 3) |

| #define ULCR_STOP_1 (0 << 2) |

| #define ULCR_STOP_2 (1 << 2) |

| #define ULSR_BI (1 << 4) |

| #define ULSR_ERR_MASK 0x1E |

| #define ULSR_FE (1 << 3) |

| #define ULSR_OE (1 << 1) |

| #define ULSR_PE (1 << 2) |

| #define ULSR_RDR (1 << 0) |

Referenced by uart0_ISR().

| #define ULSR_RXFE (1 << 7) |

| #define ULSR_TEMT (1 << 6) |

| #define ULSR_THRE (1 << 5) |

| #define UMCR_DTR (1 << 0) |

| #define UMCR_LB (1 << 4) |

| #define UMCR_RTS (1 << 1) |

| #define UMSR_CTS (1 << 4) |

| #define UMSR_DCD (1 << 7) |

| #define UMSR_DCTS (1 << 0) |

| #define UMSR_DDCD (1 << 3) |

| #define UMSR_DDSR (1 << 1) |

| #define UMSR_DSR (1 << 5) |

| #define UMSR_RI (1 << 6) |

| #define UMSR_TERI (1 << 2) |

| #define VIC_AD0 18 |

Referenced by ADC_Init().

| #define VIC_AD1 21 |

| #define VIC_ARMCore0 2 |

| #define VIC_ARMCore1 3 |

| #define VIC_BIT | ( | chan | ) | (1 << (chan)) |

Referenced by ADC_Init(), timer2_init(), and uart0_init_IRQ().

| #define VIC_BOD 20 |

| #define VIC_CAN 19 |

| #define VIC_CAN1_RX 26 |

| #define VIC_CAN1_TX 20 |

| #define VIC_CAN2_RX 27 |

| #define VIC_CAN2_TX 21 |

| #define VIC_EINT0 14 |

| #define VIC_EINT1 15 |

| #define VIC_EINT2 16 |

| #define VIC_EINT3 17 |

| #define VIC_ENABLE (1 << 5) |

Referenced by ADC_Init(), timer2_init(), uart0_init_IRQ(), and uart0_start_stop_IRQ().

| #define VIC_I2C0 9 |

| #define VIC_I2C1 19 |

| #define VIC_PLL 12 |

| #define VIC_PWM 8 |

| #define VIC_PWM0 8 |

| #define VIC_RTC 13 |

| #define VIC_SPI 10 |

| #define VIC_SPI0 10 |

| #define VIC_SPI1 11 |

| #define VIC_TIMER0 4 |

| #define VIC_TIMER1 5 |

| #define VIC_TIMER2 26 |

Referenced by timer2_init().

| #define VIC_TIMER3 27 |

| #define VIC_UART0 6 |

Referenced by uart0_init_IRQ().

| #define VIC_UART1 7 |

| #define VIC_USB 22 |

| #define VIC_WDT 0 |

| #define VICDefVectAddr (*((volatile unsigned long *) 0xFFFFF034)) |

| #define VICFIQStatus (*((volatile unsigned long *) 0xFFFFF004)) |

| #define VICIntEnable (*((volatile unsigned long *) 0xFFFFF010)) |

Referenced by ADC_Init(), timer2_init(), timer_init(), and uart0_init_IRQ().

| #define VICIntEnClr (*((volatile unsigned long *) 0xFFFFF014)) |

Referenced by EnterISPMode(), and GPIOInit().

| #define VICIntSelect (*((volatile unsigned long *) 0xFFFFF00C)) |

Referenced by ADC_Init(), GPIOInit(), timer2_init(), and uart0_init_IRQ().

| #define VICIRQStatus (*((volatile unsigned long *) 0xFFFFF000)) |

| #define VICProtection (*((volatile unsigned long *) 0xFFFFF020)) |

| #define VICRawIntr (*((volatile unsigned long *) 0xFFFFF008)) |

| #define VICSoftInt (*((volatile unsigned long *) 0xFFFFF018)) |

| #define VICSoftIntClear (*((volatile unsigned long *) 0xFFFFF01C)) |

| #define VICVectAddr (*((volatile unsigned long *) 0xFFFFF030)) |

Referenced by adcISR0(), timer2_ISR(), timer_ISR(), and uart0_ISR().

| #define VICVectAddr0 (*((volatile unsigned long *) 0xFFFFF100)) |

Referenced by timer_init().

| #define VICVectAddr1 (*((volatile unsigned long *) 0xFFFFF104)) |

| #define VICVectAddr10 (*((volatile unsigned long *) 0xFFFFF128)) |

| #define VICVectAddr11 (*((volatile unsigned long *) 0xFFFFF12C)) |

| #define VICVectAddr12 (*((volatile unsigned long *) 0xFFFFF130)) |

| #define VICVectAddr13 (*((volatile unsigned long *) 0xFFFFF134)) |

| #define VICVectAddr14 (*((volatile unsigned long *) 0xFFFFF138)) |

| #define VICVectAddr15 (*((volatile unsigned long *) 0xFFFFF13C)) |

| #define VICVectAddr2 (*((volatile unsigned long *) 0xFFFFF108)) |

| #define VICVectAddr3 (*((volatile unsigned long *) 0xFFFFF10C)) |

| #define VICVectAddr4 (*((volatile unsigned long *) 0xFFFFF110)) |

| #define VICVectAddr5 (*((volatile unsigned long *) 0xFFFFF114)) |

| #define VICVectAddr6 (*((volatile unsigned long *) 0xFFFFF118)) |

| #define VICVectAddr7 (*((volatile unsigned long *) 0xFFFFF11C)) |

| #define VICVectAddr8 (*((volatile unsigned long *) 0xFFFFF120)) |

| #define VICVectAddr9 (*((volatile unsigned long *) 0xFFFFF124)) |

| #define VICVectCntl0 (*((volatile unsigned long *) 0xFFFFF200)) |

Referenced by timer_init().

| #define VICVectCntl1 (*((volatile unsigned long *) 0xFFFFF204)) |

| #define VICVectCntl10 (*((volatile unsigned long *) 0xFFFFF228)) |

| #define VICVectCntl11 (*((volatile unsigned long *) 0xFFFFF22C)) |

| #define VICVectCntl12 (*((volatile unsigned long *) 0xFFFFF230)) |

| #define VICVectCntl13 (*((volatile unsigned long *) 0xFFFFF234)) |

| #define VICVectCntl14 (*((volatile unsigned long *) 0xFFFFF238)) |

| #define VICVectCntl15 (*((volatile unsigned long *) 0xFFFFF23C)) |

| #define VICVectCntl2 (*((volatile unsigned long *) 0xFFFFF208)) |

| #define VICVectCntl3 (*((volatile unsigned long *) 0xFFFFF20C)) |

| #define VICVectCntl4 (*((volatile unsigned long *) 0xFFFFF210)) |

| #define VICVectCntl5 (*((volatile unsigned long *) 0xFFFFF214)) |

| #define VICVectCntl6 (*((volatile unsigned long *) 0xFFFFF218)) |

| #define VICVectCntl7 (*((volatile unsigned long *) 0xFFFFF21C)) |

| #define VICVectCntl8 (*((volatile unsigned long *) 0xFFFFF220)) |

| #define VICVectCntl9 (*((volatile unsigned long *) 0xFFFFF224)) |

| #define VPBDIV (*((volatile unsigned char *) 0xE01FC100)) |

Referenced by EnterISPMode(), and main().

| #define WDFEED (*((volatile unsigned char *) 0xE0000008)) |

Referenced by EnterISPMode(), and WdtFeed().

| #define WDFLAG (*((volatile unsigned long *) 0xE01FC180)) |

| #define WDMOD (*((volatile unsigned char *) 0xE0000000)) |

Referenced by EnterISPMode(), and WDTInit().

| #define WDTC (*((volatile unsigned long *) 0xE0000004)) |

Referenced by EnterISPMode(), and WDTInit().

| #define WDTV (*((volatile unsigned long *) 0xE000000C)) |

| #define YEAR (*((volatile unsigned short*) 0xE002403C)) |

1.6.3

1.6.3